Advanced Out-of-Order RISC-V Processor

Details

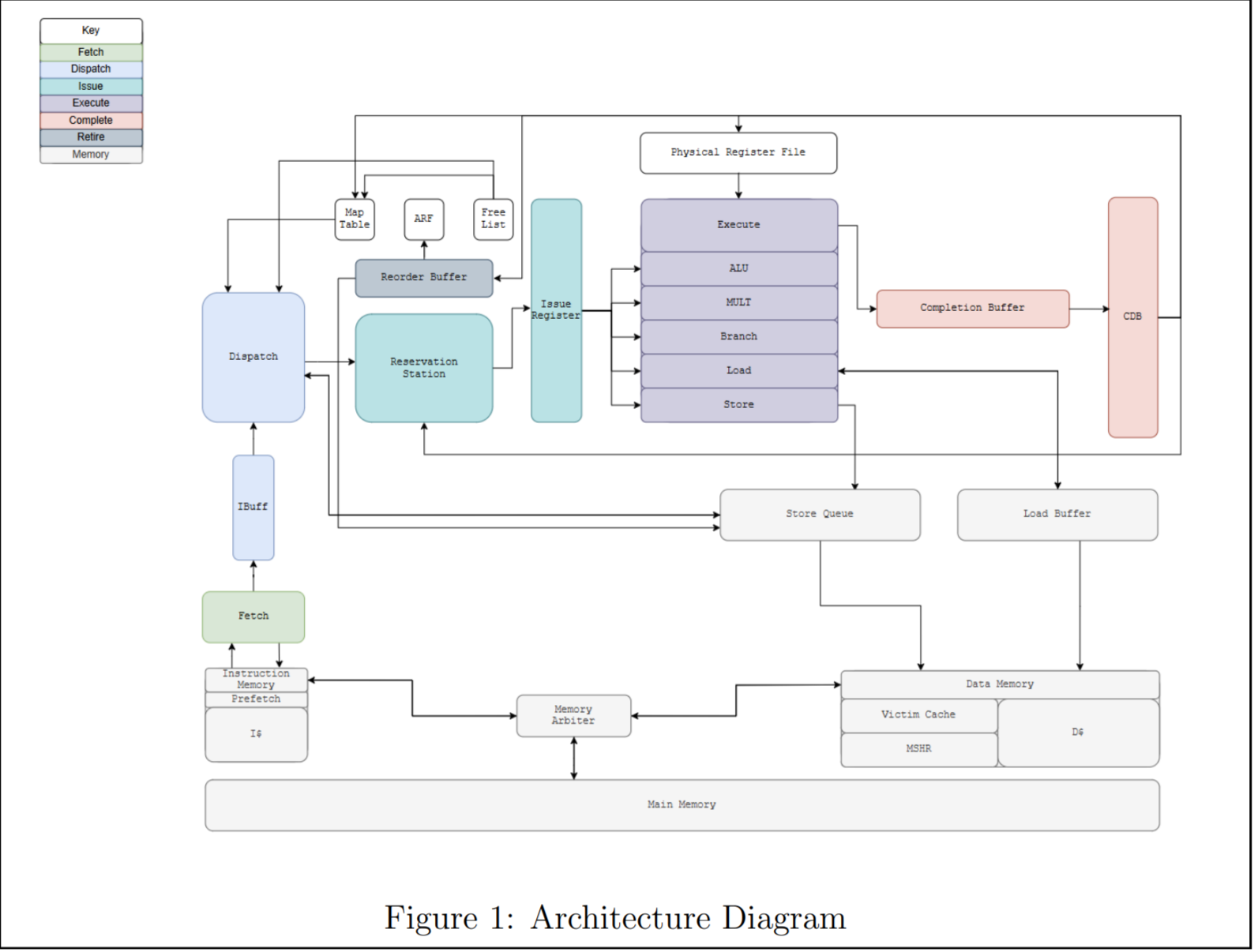

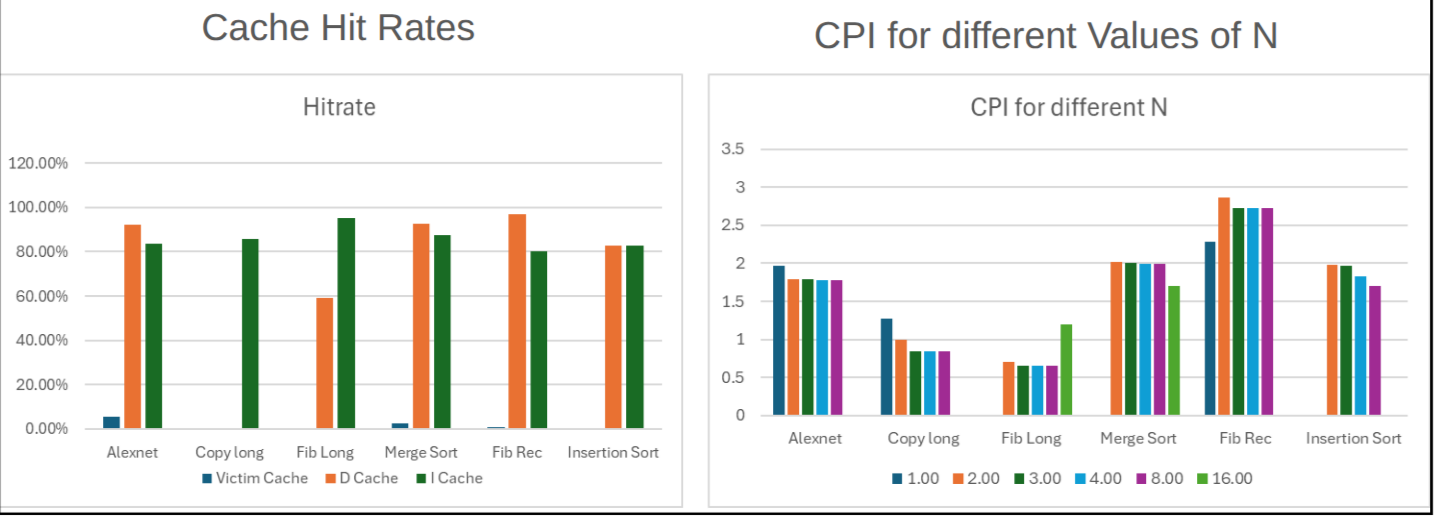

This project implements a MIPS R10K-style processor design based on the RISC-V Instruction Set Architecture (ISA), emphasizing scalability, modularity, and extensive, non-fragile unit tests. The processor is designed to achieve high Instruction Level Parallelism (ILP) while maintaining a balance between cycles per instruction (CPI) and synthesized clock period. Leveraging an N-way superscalar pipeline, the design integrates advanced features such as instruction prefetching, non-blocking data and instruction caches, and a victim cache to minimize cache miss penalties. Additionally, a Store Queue and Load Buffer were implemented to streamline memory access, reduce latency, and enhance throughput.

Our project report is available here: ooo_processor_report.pdf

Project information

- Project date 01 March, 2020