JPEG Decompression Accelerator

Details

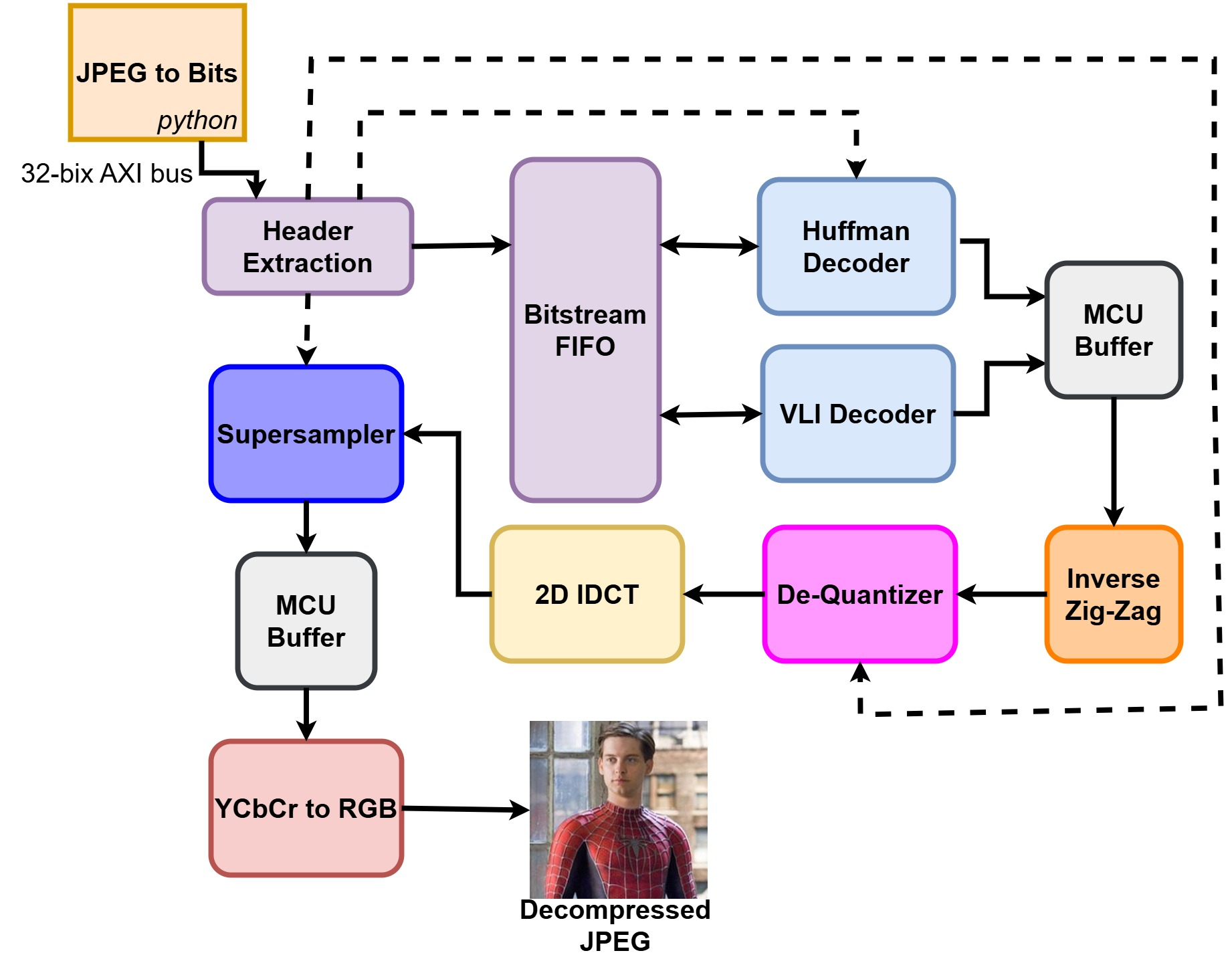

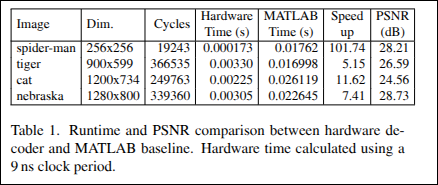

JPEG is a widely used image compression standard, but the decompression process is computationally intensive and due to its widespread usage, provides a reason for having a dedicated module in a System-on-Chip (SoC) platform. This project introduces a hardware accelerator designed to efficiently perform JPEG decompression on a mobile System-on-Chip. The design integrates key stages of the decoding pipeline—including entropy decoding, coefficient reconstruction, inverse transforms, chroma upsampling, and color space conversion—into a pipelined, and almost multiplier free architecture. The accelerator was evaluated on a variety of JPEG images and demonstrated significant performance gains compared to software-based decoding, making it well-suited for embedded and mobile applications.

Our project report is available here: JPEG_Decoding_Accelerator_Report.pdf

Project information

- Project date May 2025

- Project URL github